HILS高速化(3)FPGA

今回は、FPGAによるHILS高速化についてご説明します。FPGAを使う事で何ができるのか?を理解する事で、HILSを構築する際の、技術的な引き出しが1つ増える事になります。

さて、HILSの高速化方法ですが、CPUを使った演算をする限りは、もう限界に達してしまいました。これ以上高速化するには、FPGAに頼るしかありません。(FPGAって何?)

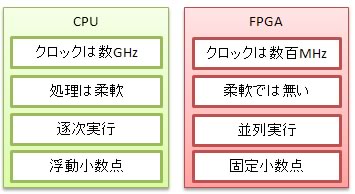

CPUは、クロックは数GHzととても高速です。それに、ソフトウェアも比較的柔軟に書く事ができます。しかし残念ながら、処理を行うのは逐次実行です。1つ1つ処理していかないといけません。

一方、FPGAというものがあります。これは、クロックは数百MHzですし(もちろん、もっと高速なものもありますが)、処理内容を柔軟に書く事も難しいです。そのかわり、処理を並列実行できます。

この並列実行という性質のおかげで、ものすごく高速に処理ができます。たとえばモデルを1マイクロ秒ステップで動かす、というのは、CPUには無理です。しかし、FPGAであればこれが可能です。

ただし、FPGAは高速に実行できる一方で、固定小数点しか扱えません。浮動小数点を扱えない事もないのですが、そうしてしまうとスピードが犠牲になってしまいます。

このように、FPGAは素晴らしいものではありますが、簡単にCPUを置き換えられるようなものではありません。

そこで今回は、FPGAをHILSに使用するための原理をご紹介します。

2つのアプローチ

FPGAを使用してHILSを高速化する際、2つのアプローチがあります。ケースバイケースでどちらが良いか変わるので、中身を理解することで使い分けが出来るようになりましょう。

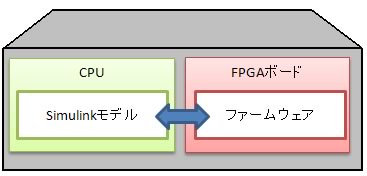

さて、2つのアプローチどちらにも共通するのは『CPUとは別にFPGAが載ったボードを用意する』という点です。CPUから見れば、FPGAは『すごく特殊なI/Oボード』のように見えます。

さて、まず1つ目のアプローチです。これは、FPGAのファームの部分を、Simulinkモデルで書いてやるという方法です。モデルのうち、ある部分はCPUで動かし、別の部分はFPGAで動かします。

もう1つのアプローチは、FPGAのファームの部分をある程度固定する方法です。ファームは基本的に変更できませんが、パラメータを与えてやる事である程度チューニングする事は出来ます。Simulinkモデルからは、FPGAのパラメータの部分だけを変更してやる形となります。

SimulinkでFPGAファームを書く(原理)

まず、FPGAの動作原理をちょっとだけ見てみます。そうすると、どういう具合にSimulinkモデルでFPGAファームが書けるのか?が納得いくようになります。

さて、ものすごく単純化して言うと、FPGAとは『レジスタ』と『論理演算』で出来ています。『論理演算』とはAND、NOT、OR、XORなどで、これらを組み合わせる事で『加算』『減算』などが実現できます。

(ちなみに、ソフト屋さんに分かりやすいようにレジスタと書きました。もうちょっと詳しく知りたい方は、『フリップフロップ』というキーワードで検索してみてください)

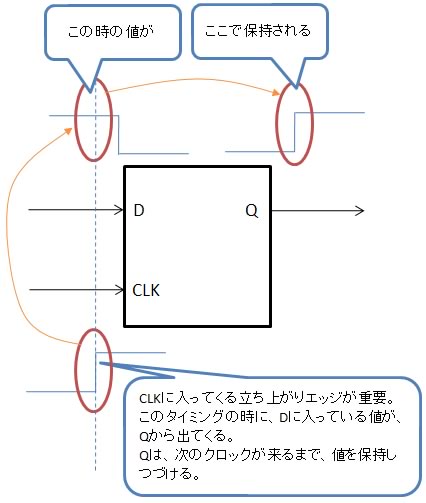

レジスタというのは、クロックの立ち上がりで出力値を確定するものです。C言語において、変数に値を代入するようなイメージです。その代入タイミングが、クロックの立ち上がりになるわけです。

こんな感じで、クロックの立ち上がりの瞬間を保持するためのものです。この入力Dには、いろいろと加算減算などをおこなった値を接続してやります。

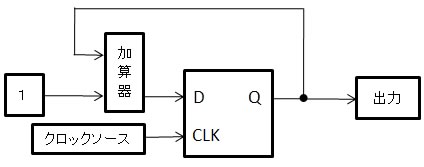

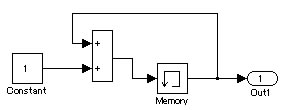

たとえば、1クロックごとにカウントアップしていくカウンターを作ってみましょう。FPGAで書くと、こうなります。

『前回の出力に1足したもの』をDポートに入力しておきます。そうすると、クロックの立ち上がりでそれが確定し、Qポートに出力されます。そうすると、クロックが立ち上がる度に、Qポートの出力が1ずつ増えて行きます。

『前回の出力に1足したもの』をDポートに入力しておきます。そうすると、クロックの立ち上がりでそれが確定し、Qポートに出力されます。そうすると、クロックが立ち上がる度に、Qポートの出力が1ずつ増えて行きます。

それでは、1ステップごとにカウントアップしていくカウンターを、Simulinkで書いて見ましょう。

こうして比べてみると分かりますが、SimulinkモデルというのはFPGAの構造とかなり似ています。どちらも、『計算する→それをメモリに保持する』という処理を、何ステップも(何クロックも)ひたすら繰り返すものだからです。

こうして比べてみると分かりますが、SimulinkモデルというのはFPGAの構造とかなり似ています。どちらも、『計算する→それをメモリに保持する』という処理を、何ステップも(何クロックも)ひたすら繰り返すものだからです。

そのため、モデルをFPGAに載せるのもそんなに難しくはありません。ただし、Simulinkモデルにおける1ステップが、FPGAにおける1クロックに相当します。これは大変な事で、FPGAが高速動作する理由になっています。

SimulinkでFPGAファームを書く(ツール)

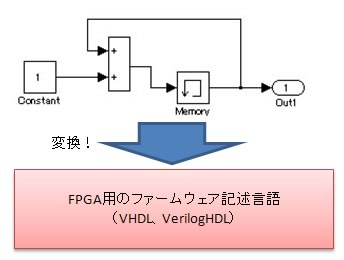

SimulinkでFPGA用のファームを書くツールには、The MathWorksが出しているものと、FPGAベンダー(XilinxやAltera、Latticeなど)が出しているものがあります。

The MathWorksが出しているツール『HDL Coder』では、SimulinkモデルをそのままFPGA用のファームウェア記述言語である、VHDLやVerilogHDLに変換することができます。

ただし、全てのSimulinkブロックを無条件にVHDLに変換できるわけではありません。あくまで、限られたブロックのみが対応しています。

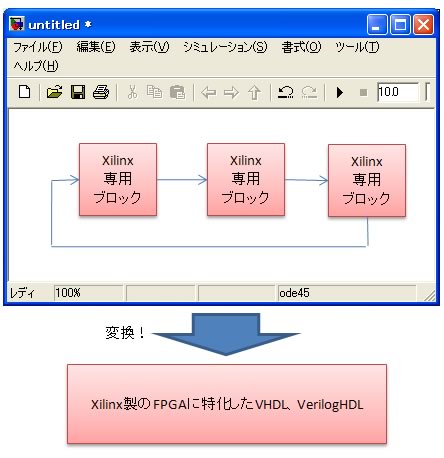

XilinxやAlteraなどが作っているツールは、これと似ています。違う点といえば、Simulinkのブロックではなく、Xilinx等が用意した特殊なブロックを使う、という点です。

これらの『専用ブロック』というのは、Simulink上でシミュレーションが出来ます。その上、FPGA上の要素と1対1対応しているため、非常にストレートにFPGAまで落ちてきます。

私は、HILS用ではないのですが、この手のツールを使ってシステムを構築した事があります。XilinxのFPGAと、上記のXilinxのツールを使って、モデルを作ります。それを、専用に起こしたボードに焼きこんで、動作させるというシステムです。そのシステムは無線通信アルゴリズム研究用だったのですが、無線アルゴリズムというのはSimulinkととても相性が良いです。そこで、Simulink上で設計をして、テストパターンなども流してある程度検証します。その上でボタン1つでFPGAまで焼きこめる、というシステムにしました。とても動作が安定していた上に、Simulink上でアルゴリズム検証が出来る、というのは非常に使い勝手の良いものでした。

このシステムを作るよりも以前、私はXilinx、Altera、Latticeの3社のデバイスを対象に、VHDLを直接手書きして、とある処理を行うためのファームウェアを作った事があります。どのベンダーでも同じなのですが、作業工程としては、『VHDLを書く』→『PC上のシミュレータでVHDLを動かす』→『VHDLをFPGA向けにコンパイルする(コンパイルすることを、FPGAの世界では論理合成・配置配線といいます)』→『実機に焼いて、動作を確認する』という手順を踏みます。

この『PC上のシミュレータでVHDLを動かす』というのが、ロジアナで波形を見るような感じで動作を追う事が出来、便利でありました。しかし、そのための入力波形は手で定義しなければいけないため、ちょっと面倒でもありました。

その点、Simulinkベースでこの作業をおこなう場合、テストパターンはCSVファイルから流し込めますし、その結果もMATLABで分かりやすく解析する事が出来ます。

生のVHDLを手書きするのと、Simulinkベースで開発するの、両方とも経験して思うのは、Simulinkベースの方が遥かに生産性が高い、という点です。もちろん使いどころによって、手書きの方が有利な点も多々あるのですが、少なくともHILS向けに使おうというレベルであれば、Simulinkベースの方がはるかに有利だと思います。

さて、SimulinkベースでFPGAのファームを作れるのは良い事です。あとは、これとHILSとの融合です。しかし、この融合の部分は、HILSベンダーが対応していないと実現できません。私が知っているのは、Opal-RT社のRT-LABという製品です。この製品では、XilinxのツールをベースにHILSのロジックをFPGAで書けるようになっています。その他のベンダーでも、こういったSimulinkベースでロジックを書けるようなシステムを出しているとは思うのですが、詳しい事は分かりません。

固定されたFPGAファームを使う

FPGAにHILSのロジックを置いてやる事で、とても高速に動作します。その一方で、FPGA向けにモデルを書かないといけません。しかし、わざわざモデルを書くのが面倒な場合もあります。あるいはモデルを書いているレベルでは十分なパフォーマンスが出ず、職人芸でもってFPGAのファームを仕上げないといけない場合もあります。こういう場合には、あらかじめFPGAのファームはHILSベンダーにて作っておく、という方法を取ります。

完全にFPGAの中身を決め打ちしてしまうと、本当の専用機になってしまいます。もうちょっと汎用性をもたせたいものです。そこで、チューニングできる範囲について決めておき、チューニングパラメータはSimulinkモデル側から設定してやれるようにします。こうする事で、FPGAの高速性を実現しつつも、ユーザー側のモデルとしてはシンプルなものになります。ある程度やる事が決まっているのであれば、このレベルが楽かと思います。

まとめ

FPGAは高速な半面、使いづらいものでもあります。そこで、どうしても高速化したいもののみをFPGA化する事になります。そのためには、

・SimulinkベースでFPGA用のロジックを書く

・手書きでFPGAの中身をHILSベンダーに作ってもらい、微調整だけ出来るようにしてもらう

の2通りの方法が考えられます。

次回

今回までは、基本的な部分を一般論のみでご説明してきました。もうそろそろ具体的な話があっても良いかと思います。というわけで次回は、方向性をガラリとかえて新しいプロジェクトを始めます。